高速仿真

随着5G的到来,随着芯片数字I/O频率不断提高,I/O互联的寄生效应变得不可忽略。这种寄生效应使数字I/O切换在互联上传输呈现电磁波的特性,使互联由低频集总参数系统变为高频分布参数系统。因此产生了高频特性和电磁波特性,使芯片I/O接收到的产生畸变,影响系统的功能、性能、可靠性。高速的研究范围主要是:高速数字系统的物理层设计,重点是电气层,了解逻辑层。芯片数字I/O及其时序/电气设置,芯片数字I/O互联:封装、PCB、连接器、线缆等。随着数字系统的高速率,低功耗的需求,伴随而来的完整性(反射/损耗/串扰/SSN/时序)等越来越突出。

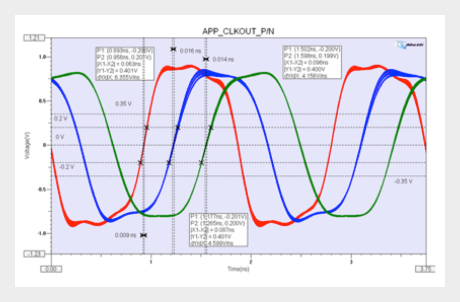

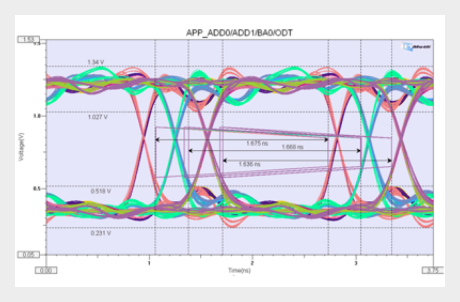

1. DDR系列完整性

基于仿真模型(IBIS,SPICE 模型等),通过仿真验证评估 DDR 质量,如过冲、振铃、单调性、噪声裕量、ISI(码间干扰)等,对于拓扑结构进行优化,并结合仿真结果给出改善方案。

-

DDR3时钟

-

DDR3地址

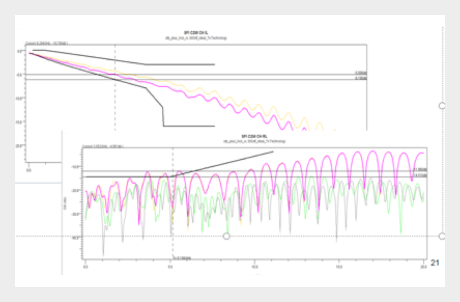

2. 高速SerDes无源链路

-

SerDes无源分析

-

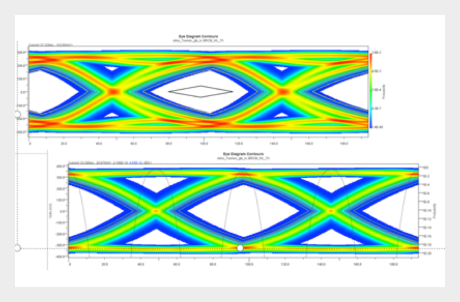

眼图/误码率分析